台積電拚2030年完成1奈米製程 單一封裝電晶體衝上1兆個

Tag

台積電 (2330-TW)(TSM-US) 在 IEDM 2023 會議中,揭露 1 奈米最新進展,預計 2030 年前會完成開發 1 奈米 (A10) 製程技術,且預期隨著先進封裝技術不斷進步,屆時將打造出內含 1 兆個電晶體的單一封裝體。

外媒指出,台積電此次重申開發 2 奈米技術 (N2/N2P),也揭露 1.4 奈米 (A14) 和 1 奈米 (A10) 的技術規劃時程,預計 2030 年前完成研發,屆時單晶片電晶體會超過 2000 億個。

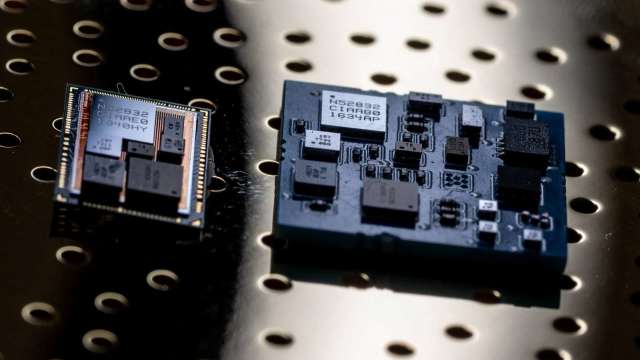

此外,台積電也看好,隨著先進封裝技術如 CoWoS、InFO 與 SoIC 等不斷進步,將在 2030 年左右打造出含有超過 1 兆個電晶體的多晶片封裝解決方案。

台積電認為,輝達 (NVDA-US) 的 GH100 是目前市面上最複雜的處理器之一,電晶體超過 800 億個,但很快就會有超過 1000 億個電晶體的晶片問世,並預期打造強大效能的處理器會越來越複雜、昂貴,因此客戶會選擇採用堆疊多晶片,預期該趨勢將延續下去。

台積電舉例,包括超微 (AMD-US) 的 MI300X 和英特爾 (INTC-US) 的 Ponte Vecchio,皆是採用數十顆晶片堆疊而成。