科林研發推全球首款晶邊沉積解決方案 提升3D晶片良率

科林研發 (Lam Research)(LRCX-US) 今 (28) 日宣布推出 Coronus DX,為業界首款最佳化的晶邊沉積解決方案,旨在解決下一代邏輯晶片、3D NAND 和先進封裝應用中的關鍵製程挑戰。

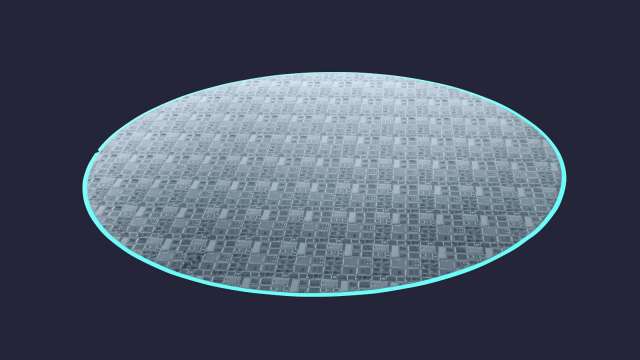

科林研發指出,隨著半導體不斷地微縮,晶片製造變得越來越複雜,在矽晶圓上建構奈米級元件需要數百個製程步驟。僅需一個步驟,Coronus DX 即可在晶圓邊緣的兩側沉積一層專有的保護膜,有助於防止在先進半導體製程中經常發生的缺陷和損壞。

科林研發 Coronus DX 可提高良率,並使晶圓廠能夠導入新的先進製程生產下一代晶片;Coronus DX 是 Coronus 產品系列的最新成員,擴展晶邊技術的領先地位。

全球產品事業群資深副總裁 Sesha Varadarajan 表示,在 3D 晶片製造世代,生產過程複雜且成本高昂。基於公司專精的晶邊創新,Coronus DX 有助於驅動可預測的製造和大幅提高良率,讓以前不可實現的技術,可導入於先進邏輯晶片、封裝和 3D NAND 生產製程。

沉積在製程整合過程中增加關鍵保護,與 Coronus 晶邊蝕刻技術互補,晶圓廠可採用新的元件結構,重複製程會導致殘留物和微粗糙沿著晶圓邊緣積聚,它們可能會剝落、漂移到其他區域並產生導致元件失效的缺陷。

科林研發舉例,在 3D 封裝應用中,來自後段的材料可能會移轉,並在未來的製程中成為污染源,晶圓邊緣的輪廓塌邊會影響晶圓接合的品質;製造 3D NAND 所需的長時間濕式蝕刻製程可能會導致晶圓基板的邊緣造成嚴重損壞,當這些缺陷不能被蝕刻掉時,Coronus DX 會在晶邊沉積一層薄的介電保護層。精確和可調控的沉積有助於解決這些可能影響半導體品質的常見問題。

CEA-Leti 半導體平台部門負責人 Anne Roule 表示,CEA-Leti 運用其在創新、永續技術解決方案上的專業知識,幫助科林研發因應先進半導體製程方面的關鍵挑戰,透過簡化 3D 整合,Coronus DX 促使良率顯著提升,使晶片製造商能夠採用突破性的生產製程。

科林研發補充,公司透過專有製程推動客戶良率提升,Coronus DX 實現一流的精密晶圓置中定位和製程控制,包括整合量測,以確保製程的一致性和可重複性,在每個蝕刻或沉積步驟中增加 0.2% 至 0.5% 的良率,可使整個晶圓生產流程的良率提高多達 5%。每月生產超過 10 萬片晶圓的製造商,在使用 Coronus 後,一年中可額外產出數百萬個晶粒,其價值高達數百萬美元。

科林研發 Coronus 產品系列 2007 年首次推出,被各大主要半導體製造商採用,在全球共安裝了數千個腔體,是業界首款經過大量生產驗證的晶邊技術。 Coronus 和 Coronus HP 解決方案是蝕刻產品,旨在透過去除邊緣層來防止缺陷,被用於製造邏輯晶片、記憶體和特殊元件,包括先進的 3D 元件。Coronus DX 現正被用於全球領先客戶晶圓廠的大量製造。

Kioxia Corporation 記憶體製程技術總監 Hideshi Miyajima 博士表示,透過晶邊技術的進步提高生產過程的品質,對於向客戶提供大規模的下世代快閃記憶體至關重要。

科林研發總經理郭偉毅博士指出,生產製造環境日益複雜,提升晶片良率已成為各家晶圓廠產量最大化的關鍵。對於開發如 Coronus DX 這樣的創新解決方案,以及推動晶片製造商生產流程改進技術而言,如何與我們客戶保持密切合作至關重要。