先進IC測試的結構性質變

AI/HPC 晶片測試針腳數倍數增長,加上高壓、高電壓、高溫與更大的封裝尺寸,讓後段測試技術提升,台系供應鏈享地利之便,迎接市占與價格雙升行情。

【文/林麗雪】

不管是 GB200 或下半年將量產的 GB300,複雜度大為提高的 AI 及 HPC 晶片正進入快速出貨期,為確保每顆晶片的良率,半導體後段測試的要求標準愈來愈高,測試產業的TAM(整體潛在市場)也正隨著AI需求而快速擴張。外資高盛指出,半導體測試產業正隨著晶片往更先進製程節點邁進而出現全面性的結構轉變,未來幾年營運成長可期。國內後段測試設備供應商包括鴻勁、致茂、探針卡廠旺矽及測試 Socket 廠穎崴,正享有地緣優勢,市占率擴張可期,成為這股結構趨勢轉變下的最大受益者。

AI晶片非先進測試不可

高盛指出,半導體晶片正變得更聰明、運作速度更快、晶片的設計製造也變得更複雜,但沒有先進測試,即便是最強大的AI晶片也會失敗。而隨著 AI/HPC 晶片採用更複雜的設計、且追求更高效能,為了確保晶片的產出及良率,測試需求的標準也大幅提高,包括接點更多、速度更快及測試公差更嚴格等,這些愈加嚴苛的測試標準,是半導體晶片測試的新挑戰,也是拉動測試產業出現結構性趨勢成長的關鍵。

尤其是對 AI/HPC 晶片來說,由於採用先進製程與封裝技術,晶片成本大幅提升,因此高品質的晶圓與晶片級測試變得極為重要,這也推動市場對更細間距與更高針腳數的探針卡(Probe Card)與測試 Socket 需求。

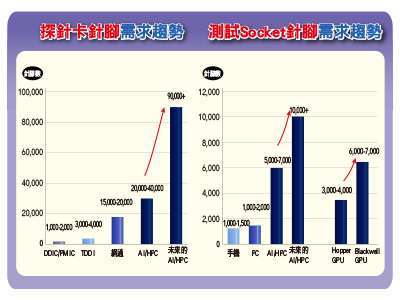

而在半導體測試環節中,針腳數(Pin)是決定探針卡(Probe Card)及測試 Socket 定價最重要的因素之一,針腳數愈高,測試單價就愈貴。據統計,目前 AI/HPC 用的測試 Socket 平均需要五○○○~七○○○個針腳,而PC僅約需要一○○○~二○○○個,智慧手機則約一○○○~一五○○個;至於探針卡(Probe Card),AI/HPC 平均約需二萬~四萬個針腳,而消費性晶片如 DDIC 或 PMIC 僅需一○○○~二○○○個,TDDI 則約三○○○~四○○○個,顯見 AI 及 HPC 晶片需要測試的電氣訊號數量直線飛漲。

再者,測試針腳數量增加與晶片的複雜度提升,也帶來了新的測試挑戰,包括高壓力、高電壓、高溫與更大的封裝尺寸,對供應鏈都是新的技術考驗。以高壓力來說,單一針腳對晶圓施加約五克的壓力,隨著針腳數增加至二萬個,可能會產生高達一○○公斤的接觸力,在測試時對晶圓表面產生更大的壓力下,可能導致晶圓損傷,因此,探針卡的機械設計也必須跟著升級,並平均分散壓力到晶圓表面,且針腳也必須設計為超低壓力,才能符合需求。

測試介面價格將翻漲一倍

此外,AI/HPC 晶片需要處理龐大的運算工作,功率需要高達二千瓦以上,以及承受較高的電壓,在測試中,探針卡必須具備高電流承載能力,才能安全的傳導大量電流而不過熱或燒毀,若不足,將導致測試結果不穩定、停機時間增加並造成成本增加。(全文未完)

來源:《先探投資週刊》2355 期

更多精彩內容請至 《先探投資週刊》